文章编号: 2096-1618(2018)03-0268-06

# 基于 FPGA 的同步机轴角编码器

张俊霞, 佘 勇, 漆 洋, 丁 晗, 刘 洁, 王 鑫 (成都信息工程大学电子工程学院,四川 成都 610225)

摘要:设计了一种基于 FPGA 的适用于伺服系统的同步机轴角编码器,实现了同步机旋转角度的测量与输出, 其通过对旋转变压器输出的两路正交调制信号与激励信号进行混频解调,得出轴相位。首先进行了原理的分析, 然后基于 FPGA 系统实现了 AD 采样、数字混频、低通滤波、CORDIC 解算、数据的串口发送等功能。最后结合旋转 变压器,在50 Hz工频载波下进行了测试。结果表明,该轴角编码器测量精度较高、数据更新快、工作稳定。

关键词:同步机;轴角编码器;FPGA;CORDIC

中图分类号:TP23

文献标志码:A

doi:10.16836/j. enki. jeuit. 2018. 03. 008

### 0 引言

角位移的测量是伺服控制系统中的一个重要环节,它的测量精度与控制系统的性能有直接的关系,改进角度测量手段对提高加工精度和科学研究等方面都有十分重要的意义<sup>[1-3]</sup>。

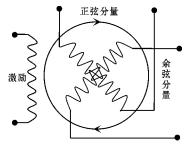

旋转变压器简称"旋变",主要用于运动伺服控制系统中测量角度位置。旋转变压器是一种把转子的角信息转换成与之对应的电信号的传感器,需要设置外围电路为其提供激励信号才能正常工作,且经过旋变输出的信号是复杂的模拟信号,需要经过处理转换为数字角度信号才能进入控制系统,其工作原理与输出的信号如图 1、图 2。旋转变压器解码是将其旋变产生的正余弦模拟信号转换为数字信号的角位置信息,解码方法一种是专门为旋转变压器设计的专用解码芯片<sup>[4]</sup>,通常需要较高的成本才能达到理想的精度,因此限制了其广泛应用;另一种就是利用单片机、Digital Signal Processing(DSP)或者 Field-Programmable Gate Array (FPGA)与 Analog to Digital (AD)转换芯片等分离器件搭建解码系统<sup>[5]</sup>,这种方法相对灵活且成本较低。

图 1 旋转变压器工作原理

收稿日期:2018-03-27

基金项目:国家自然科学基金资助项目(41475143)

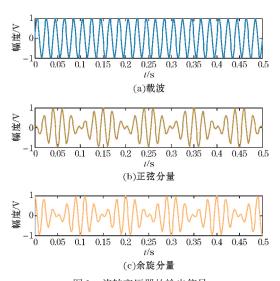

图 2 旋转变压器的输出信号

旋转变压器解码的实现通常有 2 种算法:正切算法和跟踪算法。跟踪算法相对可靠稳定,但是基于其复杂性,限制了其广泛的应用。正切算法通过计算旋转变压器两路输出正交信号的正切值<sup>[6]</sup>实现,该算法具有硬件结构简单,易于与数字电路集成等特点,但转换精度通常低于跟踪式器件<sup>[7]</sup>。

现有旋转变压器解码系统的研究,多基于单片机或 DSP 系统设计。单片机实现的系统中必须满足双机通讯,存在难以一体化集成的问题。利用 DSP 实现虽然可以提高精度,加快运算速度,但旋转变压器的解码算法仍然需要大量的运算,一次角度结算需要大量的指令周期完成,因此解码速度不够实时。

伴随着电子技术的快速发展和进步,FPGA 在数字信号处理领域得到了广泛的应用,现有 FPGA 处理器为旋转变压器解码系统的设计提供丰富的资源。如果将 FPGA 并行处理能力充分利用起来,选择合适的解码算法,既可保证解码精度,又可极大提高数据处理

的实时性。在 FPGA 的编程实现中,可采用 CORDIC (coordinate rotation digital computer)算法实现反正切操作,这种设计很适合解码这种实时性要求很高的系统,其流水线操作方式可以提高执行速度,且能以较低的成本实现系统要求。

### 1 理论分析

轴角编码器主要由信号产生和信号处理两部分组成,功能是将送入 FPGA 搭建的解码系统中的旋转变压器输出的包含角度信息的模拟信号进行解码,得到角度信息。设计中,采用50 Hz市电经过变压器的信号作为同轴电机的激励信号,同轴电机受50 Hz载波调制输出两路正交调幅信号,FPGA 控制 AD 对该三路信号的数据进行采集、解调、滤波处理得到正交的基带信号,最后采用 CORDIC 算法对两路正交基带信号执行反正切处理,获得角度信息值。

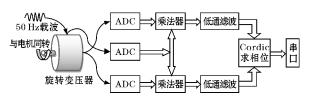

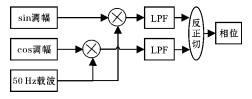

FPGA 处理包括: AD 采样、混频、低通滤波和反正切处理。首先将旋转变压器的输出信号利用 AD 转换器进行同步采集,转换为处理器可处理的数字信号,再经两路乘法器获得基带信号及载波信号,将其送入设计的数字低通滤波器中,得到两路正交的调制信号,然后将这两路正交信号进行反正切处理,最终得到需要的相位波形。利用旋转变压器测量角度位置原理如图 3所示。

图 3 利用旋转变压器测量角度原理

旋转变压器需要输入交流信号作为激励信号,输入频率范围由待测电机的转动速度决定,其输出则由两个正交的转动感应线圈控制,输出两路正交调幅信号,幅度受电机转动的调制。在转动速度不高的情况下,使用50 Hz市电经过变压器输出作为同轴电机的激励信号。同轴电机输出与激励输入信号频率一致的两路正交调幅信号,这两路调幅信号分别与载波信号相乘,经低通滤波器滤掉高频,获得正交基带信号,再经反正切算法得到角度值。其原理如图 3 所示,算法实现步骤如下。

激励信号作为同步电机的输入,同时作为信号处理的载波,设输入激励信号为

$$x = \sin(\omega t)$$

经同步电机调幅后输出的两路正交信号为

$$\begin{cases} y = \sin(\alpha t) \cdot \sin(\omega t) \\ y_1 = \cos(\alpha t) \cdot \sin(\omega t) \end{cases}$$

解调时,将两路信号分别与载波相乘:

$$\begin{cases} y = \sin(\alpha t) \cdot \sin^2(\omega t) = \frac{1}{2}\sin(\alpha t) (1 - \cos(2\omega t)) \\ y_1 = \cos(\alpha t) \cdot \sin^2(\omega t) = \frac{1}{2}\cos(\alpha t) (1 - \cos(2\omega t)) \end{cases}$$

对  $y_y$ 1 两路信号进行低通滤波处理,即可得出正交的基波输出:

$$\begin{cases} y = \sin(\alpha t) \\ y_1 = \cos(\alpha t) \end{cases}$$

通过反正切计算,提取基波信号的相位

$$\theta = \arctan(y, y_1)$$

θ即为旋转变压器轴所对应的位置信息。轴角测量的核心是如何解码旋转变压器输出的信号得到角度信息值,即反正切值的计算。反正切函数的实现有很多种方式,因此选择合适的反正切算法尤为关键。

反正切值计算可基于查表法实现,这种存储角度和与之相对应的正切数值的方法计算简单、易于实现,但占用的硬件资源多、执行速度慢,计算精度低。基于FP-GA的 CORDIC 算法,只需要使用简单的加法器和移位器,无需复杂的运算电路,便可以实现反正切运算。

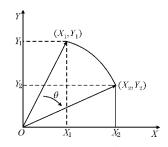

CORDIC 算法是一种坐标旋转的方法<sup>[8]</sup>,原理如图 4,其基本思想是用一系列微角度旋转逼近真实角度<sup>[9]</sup>。这种算法是把向量旋转运算转变成一系列加、减和移位运算的循环迭代算法,非常适合在硬件电路上实现,不仅可以节约硬件资源,还能大大提高计算精度和速度,可以满足实际应用中的计算需求<sup>[10-12]</sup>。

图 4 CORDIC 坐标旋转原理

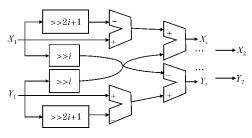

图 5 Verilog 数字实现结构

向量  $(X_1, Y_1)$  到  $(X_2, Y_2)$  可以看作是通过叠加 N 个微转角  $\theta_i$ ,所有微转角的和就是旋转过的角度  $\theta$ ,

即  $\theta = \sum_{i=0}^{N-1} \delta_i \theta_i (\delta_i \text{ 顺转为} - 1, 逆转为 1),$ 每一步微转角  $\theta_i$  的正切值表示为  $\tan \theta_i = 2^{-i}$ ,则向量  $(X_1, Y_1)$  和  $(X_2, Y_2)$  的关系可表示为

$$\begin{bmatrix} X_2 \\ Y_2 \end{bmatrix} = \prod_{i=0}^{N-1} \frac{1}{\sqrt{1+2^{-2i}}} \begin{bmatrix} 1 & -\delta_i 2^{-i} \\ \delta_i 2^{-i} & 1 \end{bmatrix} \begin{bmatrix} X_1 \\ Y_1 \end{bmatrix}$$

进行迭代计算:

$$\begin{cases} X_{i+1} = X_i - \delta_i \cdot Y_i \cdot 2^{-i} \\ Y_{i+1} = Y_i + \delta_i \cdot X_i \cdot 2^{-i} \end{cases}$$

如此, CORDIC 算法就将坐标旋转转换为只有移位和加减法的运算, 实现如图 5 所示。当  $N\to\infty$ ,  $\prod_{i=0}^{N-1} \frac{1}{\sqrt{1+2^{-2i}}} \to 0.607253$ 为一固定系数, 不影响反正切计算结果。

### 2 系统的硬件设计即 FPGA 实现

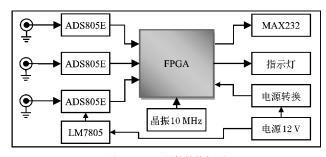

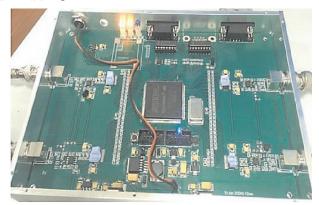

轴角编码器的硬件电路主要由 FPGA 最小系统、AD 采样电路、电源电路、串口通讯等组成,如图 6 所示。FPGA 是该系统的核心,控制 AD 采样电路,实现对轴角模拟信号的采样,并对采样数据进行混频、滤波等处理和反正切计算,求出角度值,最终将数据发送至PC 端。

设计中整个硬件系统的电源采用12 V供电,分别产生模拟电路电源和数字电路电源。其中,12 V电源经 LM2596 开关电源芯片转换成5 V,5 V再经稳压转换成3.3 V、1.2 V、2.5 V给 FPGA 供电。为降低干扰,模拟电路部分的供电采用12 V电源经 LM7805 线性稳压后的5 V电源。

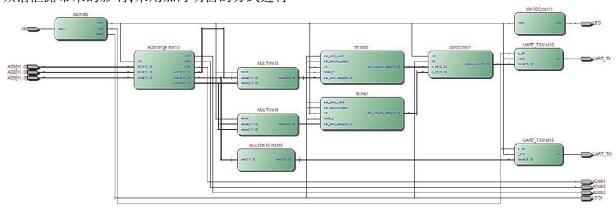

FPGA 芯片使用 Altera 公司的 Cylone III 系列芯片 EP3C25Q240C8,该芯片功耗小,系统综合能力强<sup>[13]</sup>,完全可以满足本次设计的要求。FPGA 主要实现的功能有 3 路信号的采样、数字混频、低通滤波、CORDIC 算法实现及相位的串口通信如图 7。

图 6 FPGA 硬件结构框图

图 7 FPGA 功能实现框图

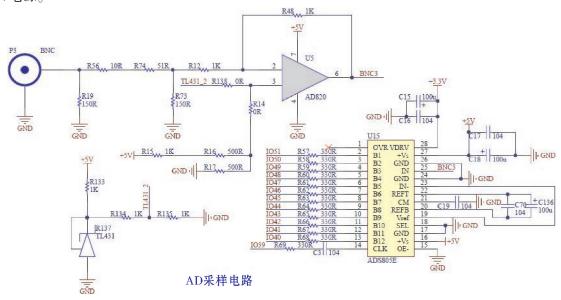

AD 采样电路设计采用 12 位高动态范围模数转换 芯片 ADS805E,该芯片高带宽、线性跟踪、特点是可以最大限度地减少谐波,低抖动<sup>[14]</sup>,且有优秀的信噪比性能。设计中一共有 3 路相同的 AD 电路,分别对激励信号和旋变电压器输出的两路正交调幅信号进行采样和转换。FPGA 通过时钟对 ADC 进行控制,激励信号和旋转变压器输出的调幅信号首先经过 π 型衰减,后由运放器 AD820 对信号进行抬升(例如:-1~1 V抬升至后为 0~2 V),作为 ADC 的输入信号。前端信号调理电路与 AD820 采样电路如图 8 所示。

图 8 输入信号调理及 AD 采样电路

整个系统设计以 Quartus II 为平台,以 verilog 语言结合原理图的方式进行设计。系统由时钟模块、三路 AD 采样、两路乘法器、两路 FIR 低通滤波器、反正切模块等构成。其中时钟模块将输入的10 MHz信号分频为 CLK1 (1000 Hz)、CLK2 (1/115200 Hz)供串口通讯使用。

乘法器的输入数据为有符号型,三路 AD 采样分别将输入信号(0~4096)搬移至交流中心(-2048~+2047),并通过软件调零。两路乘法器分别将两路输入与载波相乘,送入低通滤波器,得到两路正交的基带信号,这两路正交信号送入反正切处理模块利用进行CORDIC 算法进行处理。

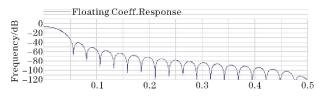

在滤波器设计过程中,根据采样率为1000 Hz下, 载波频率50 Hz,Quartus II 平台下调用 FIR 滤波器 IP 核,设置低通滤波器的通带为50 Hz,阶数为 37 阶。为 减少频谱泄露带来的影响,采用加海明窗的方式进行 滤波[15],加窗后的幅频响应如图9所示。

图 9 FIR 低通滤波器幅频响应设置,通带外衰减达到-40 dB

系统工作时,调制信号的频率范围不应超过载波频率,否则会发生频谱混叠。例如调制信号频率为55 Hz时,实际测得频率为5 Hz。根据载波频率为50 Hz,则理论上系统的最大允许检测的转速50 转/秒。另一方面,测量精度随转速的增大而降低,待测转速原则上不超过载波的频率一半较为合理,即实际使用中允许输入最大转动信号为 25 转/秒。Quartus II 平台综合后的系统如图 10 所示。

图 10 FPGA 系统功能实现框图

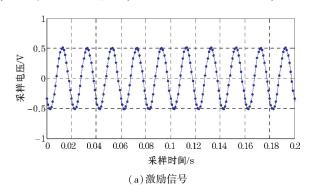

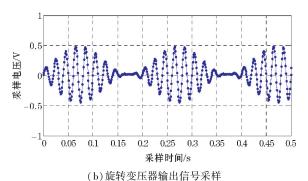

为验证系统的功能,由 MATLAB 产生 3 路信号 (载波、两路调幅信号)存入 FPGA 的 ROM 中,模拟编

码器的三路输入信号。其中,载波频率设为50 Hz,转动频率设为5 Hz,如图 11 所示。

(5) 观代文压品相目 5

图 11 激励信号与旋转变压器输出信号采样

系统运行后,使用 SignalTap 对数据抓包导出,载波的 AD 采样如图 11(a)所示,单路调幅信号 AD 采样数据如图 11(b)所示。

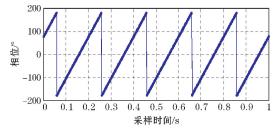

根据图 12 的相位输出结果可以看出,经过编码之后 角度相位变化从-180°~180°,变化周期为0.2 s(5 Hz), 与预设转动频率一致,这验证了解码算法设计的正确 性。

图 12 由 ROM 信号求反正切相位输出

# 3 系统测试

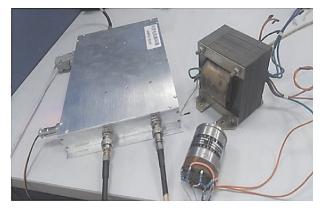

结合旋转变压器(型号为36XZ10)进行实测,首先用变压器将220 V市电变压至20 V交流信号作为旋转变压器的激励源,旋变的输出端经过电阻分压接入信号处理器,将三路输出信号接入设计的编码器进行处理。旋转变压器的两路输出经电阻分压至1 V后送入采集器。编码器和系统测试平台如图 13、图 14 所示。

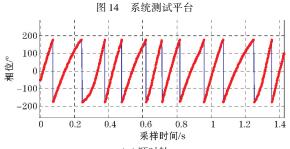

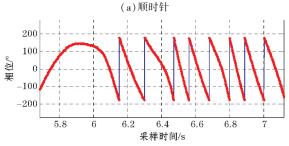

分别测试了顺转、逆转时的相位输出情况,如图 15所示。

图 13 轴角编码器成品

(b)逆时针 图 15 旋转变压器和旋转相位输出结果

在图 15(a)中,转动方向为顺时针,编码器输出的相位结果由-180°~180°循环输出。在图 15(b)中,旋转变压器的转动方向在第6 s左右开始由顺时针变为逆时针,编码器输出的相位输出由+180°~-180°循环输出。

经过对比顺转、逆转时的相位结果,均可输出-180°~180°的相位变化,且缓慢转动时相位变化缓慢,快速转动时,相位变化较快。实现结果表明,相位检测结果良好,噪声较小,测试效果良好。

# 4 结束语

提出了一种基于 FPGA 芯片、ADS805E 模数转换 芯片和 CORDIC 算法的同步机轴角编码器设计方案。 经过理论分析测量原理,并对原理进行仿真验证,然后基于 FPGA 系统实现 AD 采样、数字混频、低通滤波、CORDIC 解算、数据的串口发送等功能,最终系统实现了同步机旋转角度的测量,测试结果良好。

设计完全基于 FPGA 实现了电机转动角度的精确测量。在设计 FIR 滤波器时,由于阶数达到 37 阶,存在输入输出的纯延时问题,基于采样频率是1000 Hz, 37 个时钟延时,相当于有37 ms的延时,影响角度测量的实时性,后期可采用跟踪算法进行进改善。

在实际使用时,系统的噪声可能来自多方面,如来自电网的波动,电机转动的机械震动,AD 采样的噪声等等,这些因素都将导致相位的解算出现误差。因此,如何降低噪声对系统稳定性的影响也是本文需要完善的方向。

# 参考文献:

- [1] 秦继荣,沈安俊.现代直流伺服控制技术及其控制系统设计[M].北京:机械工业出版社,1993.

- [2] 帅浩.基于旋转变压器的角位移测量技术[D]. 太原:中北大学,2015.

- [3] 汪卓飞. 一种高精度角度传感器的研究[D]. 杭州:浙江工业大学,2009.

- [4] 刘柏林. 基于 FPGA 的旋转变压器解码算法与系统设计[D]. 重庆: 重庆大学, 2007.

- [5] 石虎威. 基于 CORDIC 算法的旋转变压器解码系统的设计[D]. 长沙:湖南大学,2012.

- [6] 张恒,冯旭升,薛东方等.基于正切算法的轴角数字转换器设计[J].军械工程学院学报,2010,22(3):40-43.

- [7] 郭宝锋,韩壮志,何强等. 基于 FPGA 的雷达天

- 线轴角编码器设计与实现[J]. 计算机测量与控制,2011,19(8):2009-2012.

- [8] 曹剑英, 葛俊峰. CORDIC 算法正切余切函数的 FP-GA 实现[J]. 数字技术与应用, 2016(8):160-161.

- [9] 孔德元. 针对正弦余弦计算的 CORDIC 算法优化及其 FPGA 实现[D]. 长沙:中南大学,2008.

- [10] 杨健,刘渝,狄慧等. 长基线带宽侧向算法及 FPGA 实现[J]. 电子测量与仪器学报,2013 (9):897-905.

- [11] 魏岳伦,岳庆英,齐庆等.基于 Nios II 的 DDS 函数信号发生器[J]. 国外电子测量技术,2016

- (7):13-16.

- [12] 高兵益,徐磊. CORDIC 算法及其展开结构的 FP-GA 实现[J]. 电子测量技术,2017(11):85-88.

- [13] 马腾. 基于 FPGA 的高性能 DAC 芯片测试与研究[J]. 通信技术,2011(2):154-156.

- [14] 卢斌. 超声波换能器谐振频率跟踪方法研究 [D]. 重庆: 重庆大学, 2012.

- [15] 曹锋,高华. 一种基于加窗的插值 FFT 重构 Hilbert 变换方法[J]. 重庆理工大学学报,2012 (2):97-100.

#### Synchronizer Axial Angle Encoder based on FPGA

ZHANG Jun-xia, SHE Yong, QI Yang, DING Han, LIU Jie, WANG Xin (College of Electronic Engineering, Chengdu University of Information Technology, Chengdu 610225, China)

**Abstract**: This paper designed a synchronizer axial angle encoder realized the measurement and output of the synchronizer rotative angle based on FPGA, which can be used in servo system. The encoder obtains the phase by mixing and demodulating the exciting signal and the two orthorhombic modulated signals from the resolver. Firstly, this paper analyzed the theory, and then achieved the functions of AD sample, digital mixing, low-pass filter, CORDIC and serial port based on the FPGA. Finally, conducted tests withthe resolverinaCarrier of 50 Hz. The results show that the encoder hashigh measuring precision, high speed of data-updating and stable working performance.

**Keywords**: synchronizer; axial angle encoder; FPGA; CORDIC